## Yamaha DA8X Modification from Y2 input to AES input

## Version: <mark>v4</mark>

## 1. Background:

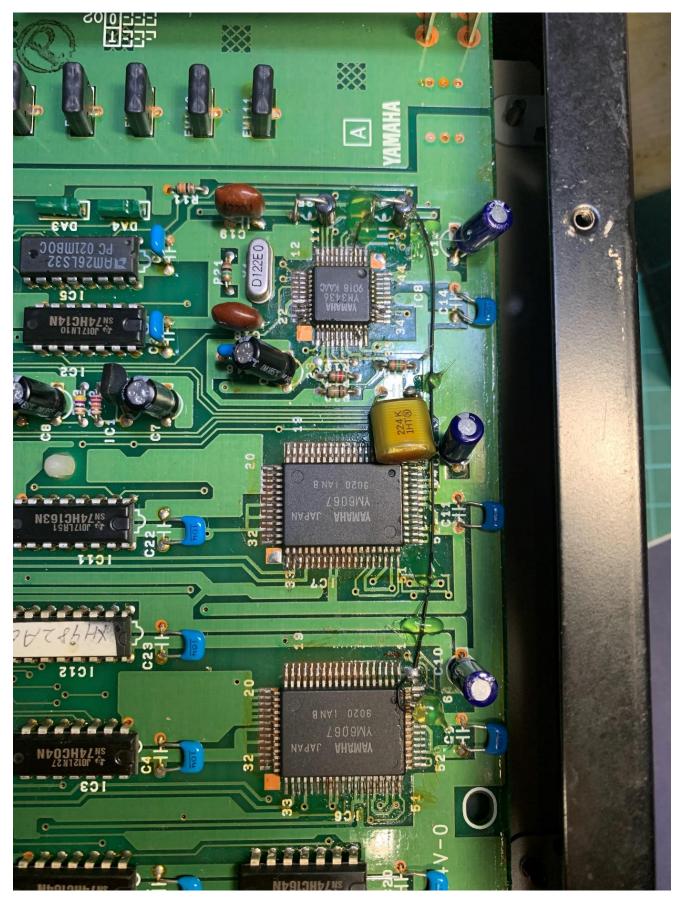

Yamaha made this DAC with digital signal input using Y2 format with D-SUB 25 female connector of 8 channels audio. It is designed for digital mixing console like DMC1000, DMP7D etc.. Thus it is not able to use for home audio environment as there is no Y2 format digital output source. Yamaha made a FMC9 format converter from AES x 4 to Y2 output via D-Sub 25 socket but is not widely available yet! In order to use it for Home audio, the digital input must be using AES/SPDIF/Toslink sockets but none of these format is build in the DA8X. Why I choose AES input digital format, as far as I know the DA8X use a DIR2 chip YM3436D at its digital input which is same as the Yamaha D2040 digital crossover. By reviewing the service manuals, it is possible to modify the digital board of DA8X to accept AES format.

## 2. Major parts in DA8X:

- 1. DIR2 chip: YM3436D this is a digital interface chip accept both AES/SPDIF and Y2 format signal widely use in Yamaha products since 1988. It is used in D2040 also.

- 2. YM6067: Parallel to Serial and serial to serial buffer x 2 chips, one chip support total 4 channels digital signal.

- 3. SM5803APT: 18 or 20 bit 8x oversample filter x 2 chips.

- 4. PCM63-KY or Y: DAC 20bit x 8 pcs; well know ladder type DAC which sound best back in 1989 period.

- 5. IV op-amp: M5238 dual op-amp.

- 6. Drivers op-amp: NE5532.

- 7. Resistor is 1/8W metal film resistors; not like D2020 use RMA resistors.

- 8. E-Capacitor: Elna Durex grade, I dissolder and verify the capacitors are still very good after 30 years.

- 9. Output couple capacitor is MUSE bi-polar Green capacitors.

- 10. Other film capacitor are either 5% or Soshin brand.

3. Target: Able to use the DAC with such good DAC chips but the digital input must be modified to common SPDIF/AES/Toslink connector. Target is to use AES as the digital board input has a line receiver chip AM26LS32. One for 4 channels data line and one delicate for one channel word clock input sync use. After tracing the signal, the work clock input is connected to EXTW input of YM3436 which is next pin to the digital input of DDIN.

4. Y2 format with D-Sub 25 female socket, out of which, also one channel Word Clock using pin 9 (+) and 22 (-). After tracing the path, it is connected to YM3436 pin 36 EXTW via AM26LS32 line receiver IC5 pin 3. The input pin 1 and 2 of AM26LS32 are connected to the D-Sub 25 pin 9 and 22.

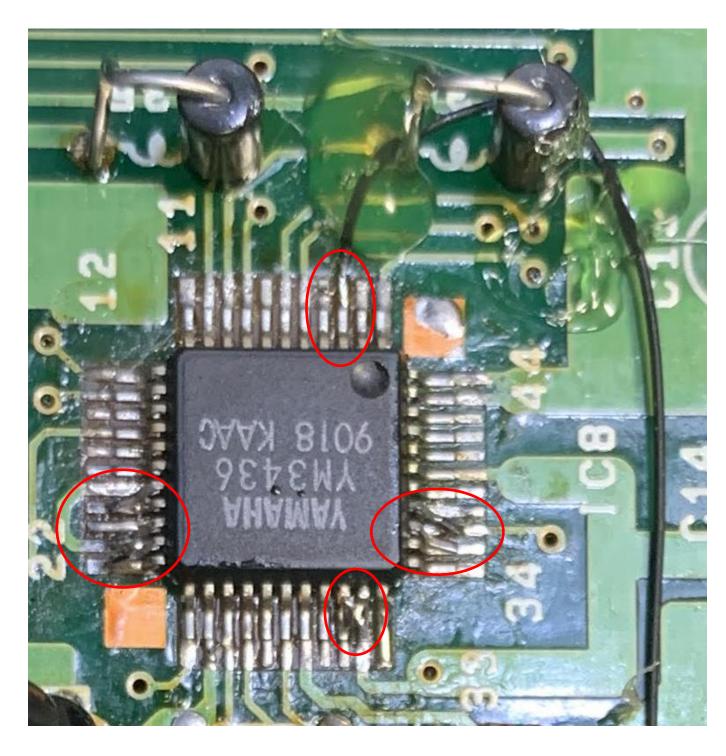

5. The DDIN of YM3436 is pin 37. Thus, first change is to (1) lift up EXTW pin 36, connect to pin 35 CSM which is grounded. So EXTW is now grounded and disable. (2) Then pin 37 DDIN of YM3436 is lift up and connected to the "pad of Pin 36". This is possible as the pin of YM3436D can be straighten and then solder to adjacent pin or adjacent solder pad as shown.

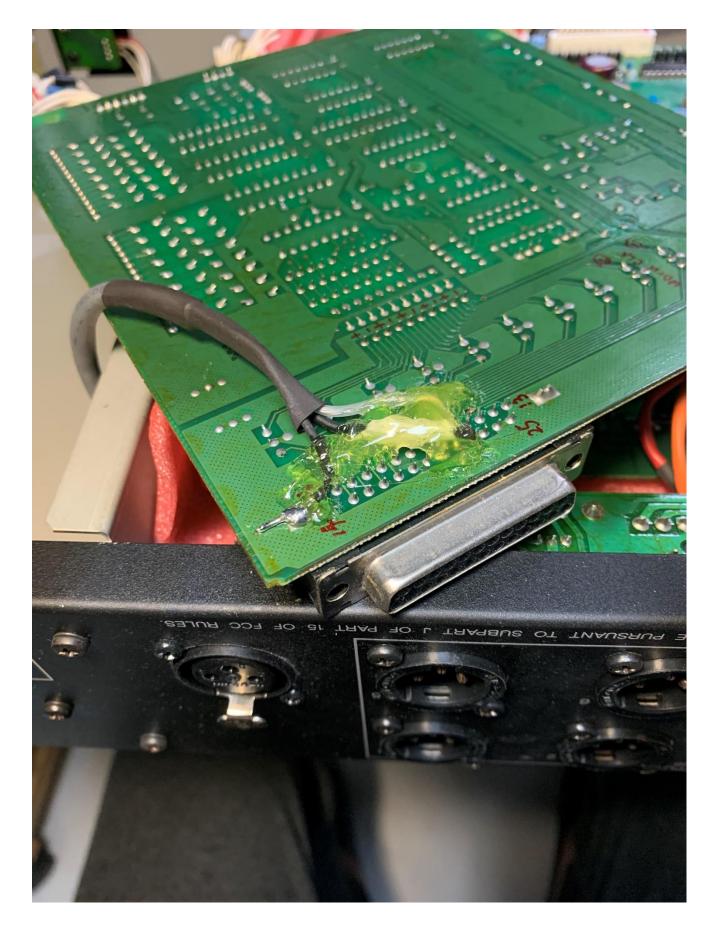

6. YM3436 pin 3 is DOUT signal (decoded from DDIN signal), it is now connected to IC6 YM6067 pin 64 and 62 (3) + (4). Note the Pin 64 and 62 must be lift up from its pad first before connecting to DDIN. There is no trace and thus a jumper wire is used. Use the square PAD next to pin 64 as support of pin 64, jumper wire to pin 62 and then hot glue all connection to prevent movement.

Note that Pin 64 and Pin 62 are the Channel 1-2 and 3-4 digital data input pins. The digital data out from YM6067 is at pin 34 and 36. It is then buffer by HC245 before goes to the connector which use a bus wires connect to DA board. Thus channel 1 is Left channel and channel 2 is R channel at the XLR audio output. Channel 3 is Left channel and channel 4 is Right channels. I did not do for all 8 channels as I think one DA board with 4 channels for me is good enough. Also there is no buffer from DOUT and I worry the driving voltage may be not enough for 4 input pins at YM6067.

7. YM3436 pin 32 is KM0 at High, it must be connected to Low (ground) to select DDIN signal. Thus (5) lift up Pin 32 and then connected to pin 31 KM2 which is connected to Ground.

| 31 | KM2 | I | Clock mode select 2 ('H'; PLL synchronized, 'L'; XI synchronized) |

|----|-----|---|-------------------------------------------------------------------|

| 32 | KM0 | 1 | Clock mode select 0 ('H'; EXTW input, 'L'; DDIN input)            |

8. YM3436 pin 18 DIM1 is at Low (ground), it is required for both DIM1 and DIM0 at High, thus (6) connect the lift pin 18 to pin 17 to high +5V of YM3436.

(1) Auxiliary input format

| DIM 1 | D1M 0 | Format     |

|-------|-------|------------|

| L     | L     | DAUX(1)    |

| L     | н     | DAUX(2)    |

| н     | L     | DAUX(3)    |

| н     | н     | DDIN input |

9. YM3436 DOM1 and DOM0: Default is High Low. Change to Low High. (7) Lift up pin 21 DOM0 and connect to Pin 22 KM1 which is at HIGH (+5V). (8) Also lift up pin 20 DOM1 and connect to the "PAD of Pin 21" which is at Low (ground). Serial data is reversed as the YM6067 will reverse it again!

(2) Data output format

| DOM 1                | DOM 0 | Format          |

|----------------------|-------|-----------------|

| L                    | L     | MCC(1), DOUT(1) |

| 1 <mark>- 1</mark> - | н     | MCC(1). DOUT(2) |

| Н                    | L     | MCC(2), DOUT(3) |

| н                    | н     | MCC(1), DOUT(4) |

|   | мсв     |                                                                                                                | นแนนแนนแนนแนนแนนแนนแนนแนนแนนแนนแนนแนนแน                                                                        |

|---|---------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|   | MCO(I)  | www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.ww | www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.ww |

|   | MCC(2)  | www.www.www.www.www.                                                                                           | www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.www.ww |

| L | wc      |                                                                                                                |                                                                                                                |

|   | DOUT(1) | MSB L-CH LSB                                                                                                   | MSB R-CH LSB                                                                                                   |

|   | DOUT(2) | LSB L-CH MSB                                                                                                   | LSB R-CH MSB                                                                                                   |

10. AES input connection:

Pin 9 and Pin 22 of D-SUB 25 socket. In fact, a female XLR connector can be install to the back of chassis and connect as below. Pin 9 connect to pin 2 of XLR, Pin 22 connect to pin 3 of XLR. The pin 1 on XLR connected to the ground plan of the D-sub 25 PCB.

11. Audio Signal output:

| Output Channel | Left Channel | Right Channel |

|----------------|--------------|---------------|

| Group 1        | 1            | 2             |

| Group 2        | 3            | 4             |

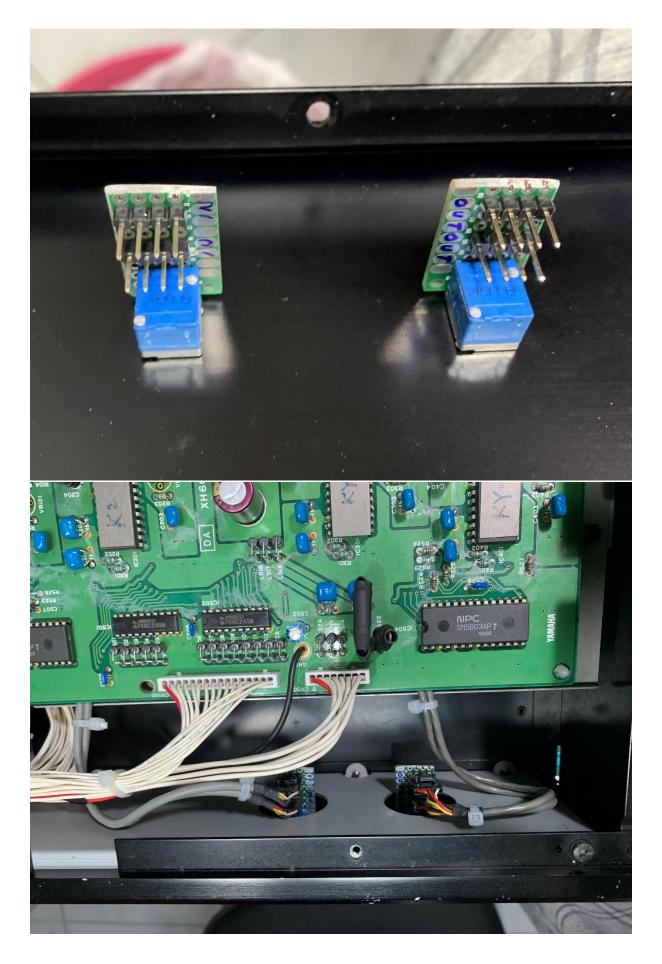

### 12. Volume Control:

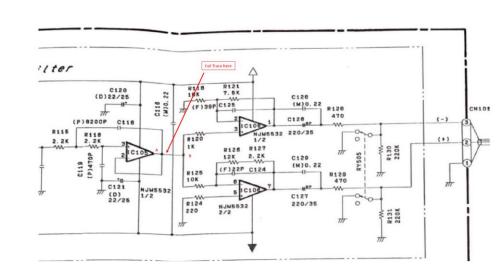

Added volume control as show in the diagram below: This idea is copied from other Yamaha gears like DEQ5, D2040 to have a volume control after the DAC. This is to prevent digital volume control to loss the bit resolutions. Other photos at the back of this document.

Volume control is 10k A type. I use a cheap Bourns PTD902-2015F-A103 from Element14. The wire is only the sound card wire in old computer one wire cut into two for two channels.

Other information:

- 1. YM6067 pins

- 2. Y2 format pin

- 3. D-Sub Y2 pin

- 4. Photo of modified set

- 5. YM3436 datasheet

- 6. Draft notes

## 1. YM6067 pins:

In fact, this chip is NOT needed if the Y2 format choose to use MSB first in the digital Data pin. The only function of the YM6067 is to reverse (pin 40 ECCO is High) the LSB first to MSB first data stream in this DA8X because PCM63 accept digital data with MSB first. Thus, I also need to modify the YM3436 to output LSB first data stream in this modification.

| • Y                                  | M6067                                                | (XF                      | 494A00) <b>PSC4</b> (Parallel Serial C                                                                                                                                                                                                                                                                                                              | Conv                 | erter)                         |             | MAIN: IC159                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN<br>NO.                           | NAME                                                 | I/O                      | FUNCTION                                                                                                                                                                                                                                                                                                                                            | PIN<br>NO.           | NAME                           | I/O         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | D23<br>D22<br>D21<br>D20<br>D19<br>D18<br>D17<br>D16 |                          | Parallel I/O ports (Doo: LSB, D23: MSB)                                                                                                                                                                                                                                                                                                             | 40<br>41<br>42<br>43 | CO1<br>Vss<br>CO0              | <br>   <br> | MSB/LSB reverse control terminal for<br>internal parallel busŮserial output. Basic<br>format is maintained when Lo. When<br>this goes Hi, the MSB/LSB are reversed.<br>Serial output selection terminal<br>Ground<br>Serial output selection terminal                                                                                                                                                        |

| 9<br>10<br>11<br>12                  | D15<br>Vss<br>D14<br>D13                             | 1/0<br>1/0               | Ground                                                                                                                                                                                                                                                                                                                                              |                      |                                |             | CO1         CO00         FORMAT           0         0         YANAHA 24-1 (1 channel/1 line)           0         1         YANAHA 24-2 (1 channel/1 line)           1         1         YANAHA 24-2 (1 channel/1 line)           1         1         YANAHA 26           1         1         YANAHA 26                                                                                                       |

| 13<br>14<br>15<br>16                 | D12<br>D11<br>D10<br>D09                             |                          |                                                                                                                                                                                                                                                                                                                                                     | 44                   | вско                           | 0           | Parallel to serial conversion clock output<br>terminal for serial output section.<br>Normally connected to SCKO.                                                                                                                                                                                                                                                                                             |

| 17<br>18<br>19<br>20<br>21           | D08<br>D07<br>D06<br>D05<br>D04                      | 1/0<br>1/0<br>1/0<br>1/0 | > Parallel I/O ports (Doo: LSB, D23: MSB)                                                                                                                                                                                                                                                                                                           | 45                   | SCKO                           |             | Parallel to serial conversion clock input<br>terminal for serial output section. Data from<br>SO0-3 is output at the rising edge of the<br>clock.<br>*The start of a word must always be a rising                                                                                                                                                                                                            |

| 22<br>23<br>24<br>25                 | D03<br>D02<br>D01<br>D00                             | 1/0<br>1/0<br>1/0        |                                                                                                                                                                                                                                                                                                                                                     | 46                   | SYNO                           | T           | edge.<br>Sync word input terminal for serial output<br>section. The start of a word is defined as<br>the third rising edge of the MCKO after                                                                                                                                                                                                                                                                 |

| 26<br>27<br>28                       | VDD<br>Vss<br>OENP                                   | T                        | Power supply<br>Ground<br>Output control terminal for parallel ports<br>D00-D15.                                                                                                                                                                                                                                                                    | 47                   | МСКО                           | I           | going from Hi to Lo.<br>Master clock input terminal for serial output<br>section. Receives 128 x fs (rising edge<br>first) clock.                                                                                                                                                                                                                                                                            |

|                                      |                                                      |                          | When Lo: internal bus → external<br>When BA0 is Hi, the impedance of the<br>parallel ports will be Hi even if this is set<br>to Lo.                                                                                                                                                                                                                 | 48<br>49<br>50       | TST<br>RESN<br>MCKI            | l           | Pin for LSI testing. Normally fixed at Lo<br>System reset terminal<br>Master clock input terminal for serial input<br>section. Receives 128 x fs (rising edge                                                                                                                                                                                                                                                |

| 29                                   | BA0                                                  | 1                        | Terminal for selecting origin of data writing<br>for the serial output section.<br>When Lo: serial input section $\rightarrow$ serial output<br>section.                                                                                                                                                                                            | 51                   | SYNI                           | I           | first ) clock.<br>Sync word input terminal for serial input<br>section. The start of a word is defined as<br>the third rising edge of the MCKI after going                                                                                                                                                                                                                                                   |

| 30                                   | MODA                                                 | ļ                        | When Hi: parallel port → serial output section<br>However, control cannot be carried out<br>except when MODA=MODB=Lo.<br>4 Internal Blocks                                                                                                                                                                                                          | 52                   | SCKI                           | 1           | from Hi to Lo.<br>Serial to parallel conversion clock input ter-<br>minal for serial input section. Data from<br>SI0-3 is received at the falling edge of the                                                                                                                                                                                                                                                |

| 31                                   | MODB                                                 | 1                        | 1: Serial Input section (SI)<br>2: Serial Output section (SO)<br>3: Buffering section (BUF)<br>4: Parallel port section (PARA)                                                                                                                                                                                                                      | 53                   | BCKI                           | 0           | clock. Normally connected to BCKI.<br>Serial to parallel conversion clock output<br>terminal for serial input section. Normally<br>connected to SCKI.                                                                                                                                                                                                                                                        |

|                                      |                                                      |                          | Terminals used to determine how<br>connections are made.           MODEMODA         Signal Path         Al0, 1: A00, 1: BAO: WTN           0         0         Si→SO         Enabled           0         1         Si→SO         Disabled           1         0         Si→SO         Disabled           1         0         Si→SO         Disabled | 54<br>55             | CI1<br>CI0                     |             | Cit         Cit         FORMAT           0         0         YAMAHA 24-1 (1 channel/1 line)           0         1         YAMAHA 24-2 (1 channel/1 line)           1         0         YAMAHA 24-2 (1 channel/1 line)           1         1         YAMAHA 24-2 (1 channel/1 line)           1         1         YAMAHA 24-2 (1 channel/1 line)           1         1         YAMAHA 24-2 (1 channel/1 line) |

|                                      |                                                      |                          | PARA       1     1     SI→BUF→SO     Disabled       PARA     Disabled     PARA   The input and output channels are the same except when MODA=MODB=Lo.                                                                                                                                                                                               | 56                   | EXCI                           | 1           | *Caution is advised when changing modes<br>dynamically. (Cl0 and Cl1 are latched at<br>the start of a word.)<br>MSB/LSB reserve control terminal for serial                                                                                                                                                                                                                                                  |

| 32                                   | OENO                                                 | 1                        | Output control terminal. Works in conjunction<br>with the serial output terminals SO0-3.<br>Output is 0 when Hi, and operation is normal<br>when Lo.                                                                                                                                                                                                | 57                   | Vss                            |             | input → internal parallel bus. Basic format is<br>maintained when Lo. When this goes Hi,<br>the MSB/LSB are reversed.<br>Ground                                                                                                                                                                                                                                                                              |

| 33<br>34<br>35<br>36                 | SO3<br>SO2<br>SO1<br>SO0                             | 0000                     | Serial data output terminals.           YAMAHA 24-1 YAMAHA 24-2 YAMAHA 45 YAMAHA 35 S00 ch 0 ch 0 ch 0 ch 0, 1 ch 0, 1, 2, 3 S01 ch 1 ch 1 x x           S00 ch 2 ch 2 ch 2 ch 2 ch 2 ch 2 x           S02 ch 3 ch 3 x x                                                                                                                            | 58<br>59<br>60       | VDD<br>AI1<br>AI0              | i           | Power supply<br>Register channel selection<br>terminals for serial input→<br>internal parallel bus output.<br>However, control cannot be carried out<br>unless MODA=MODB=Lo. When MODA                                                                                                                                                                                                                       |

| 37<br>38                             | AO1<br>AO0                                           | 1                        | Writing channel selection ter-<br>minals for internal parallel bus $\overline{0}$ $\overline{0}$ $\overline{0}$ $\overline{0}$<br>$\rightarrow$ serial output latch.<br>Control cannot be carried out<br>unless MODA=MODB=Lo.                                                                                                                       | 61<br>62<br>63       | SI3<br><mark>SI2</mark><br>SI1 |             | =MODB=Lo, each word is output 1/4 at<br>a time from channels 0, 1, 2, and 3.<br>Serial data input terminals.                                                                                                                                                                                                                                                                                                 |

| 39                                   | WIN                                                  | I.                       | Write signal to internal parallel bus → serial<br>output latch. Parallel bus data can be receiv-<br>ed in the shift out latch when Hi → Lo → Hi.<br>However, control cannot be carried out un-<br>less MODA=MODB=Lo.                                                                                                                                | 64                   | SIO                            | i           | YAMAHA 24-1         YAMAHA 24-2         YAMAHA 46         YAMAHA 55           SIO         0h 0         0h 0         0h 0, 1         0h 0, 1, 2, 3           SI1         0h 1         0h 1         x         x           SI2         0h 2         0h 2         0h 2         0h 3         x           SI3         0h 3         0h 3         x         x         x                                              |

## • YM6067 (XH494A00) PSC4 (Parallel Serial Converter)

2. Yamaha Y2 format:

Dedicated audio interfaces 221 Pin-outs WCLK + GND 3 Audio data 4 WCLK -5 Audio data + 6 20 µH coil to GND 7 20 µH coil to GND 8 GND (in), ENABLE (out) Figure 4.35 Pinouts of the Yamaha two-channel cascade interface. WCLK R channel sample data Audio data L channel sample data LSB LSB 32 32 Only 24 bits actually used per sample Figure 4.36 Data format of the Yamaha 'cascade' interface.

The two-channel cascade interface terminates in an eight pin DIN-type connector, as shown in Figure 4.35, and carries two channels of 24-bit audio data over an RS-422-standard differential line. The two channels of data are multiplexed over a single serial link, with a 32-bit word of left channel data followed by a 32-bit word of right channel data (the 24 bits of audio are sent LSB first, followed by eight zeros). The word clock alternates between low state for the left channel and high state for the right channel, as shown in Figure 4.36. Coils of  $20 \,\mu$ H are connected between pins 6 and 7 and ground to enable suppression of radio frequency interference. The OUT socket is only enabled when its pin 8 is connected to ground.

#### References

1. AES, AES3-1985 (ANSI S4.40-1985). Serial transmission format for linearly represented digital

## 3. D-SUB25 pins:

# Digital Output

| PIN No. | <u>Y1</u>            | <u>Y2</u>              |

|---------|----------------------|------------------------|

| 1       | Data CH 1, 2 OUT (+) | Data CH 1, 2 OUT (+)   |

| 2       | Data CH 2, 1 OUT (+) | Data CH 3, 4 OUT (+)   |

| 3       | Data CH 3, 4 OUT (+) | Data CH 5, 6 OUT (+)   |

| 4       | Data CH 4, 3 OUT (+) | Data CH 7, 8 OUT (+)   |

| 5       | Data CH 5, 6 OUT (+) | N/C Pass Association - |

| 6       | Data CH 6, 5 OUT (+) | N/C                    |

| 7       | Data CH 7, 8 OUT (+) | N/C                    |

| 8 .     | Data CH 8, 7 OUT (+) | N/C designed and a set |

| 9       | Word Clock OUT (+)   | Word Clock OUT (+)     |

| 10      | Word Clock IN (+) *  | Word Clock IN (+) *    |

| 11      | N/C                  | Emphasis               |

| 12      | Emphasis             | N/C                    |

| 13      | Ground               | Ground                 |

| 14      | Data CH 1, 2 OUT (-) | Data CH 1, 2 OUT (-)   |

| 15      | Data CH 2, 1 OUT (-) | Data CH 3, 4 OUT (-)   |

| 16      | Data CH 3, 4 OUT (-) | Data CH 5, 6 OUT (-)   |

| 17      | Data CH 4, 3 OUT (-) | Data CH 7, 8 OUT ()    |

| 18      | Data CH 5, 6 OUT ()  | N/C                    |

| 19      | Data CH 6, 5 OUT (-) | N/C                    |

| 20      | Data CH 7, 8 OUT (-) | -N/C                   |

| 21      | Data CH 8, 7 OUT (-) | N/C                    |

| 22      | Word Clock OUT (-)   | Word Clock OUT (-)     |

| 23      | Word Clock IN (-) *  | Word Clock IN (-) *    |

| 24      | Ground               | Ground                 |

| 25      | Ground               | Ground                 |

| CASE    | Frame Ground         | ·                      |

\* Not used by the FMC9. N/C : No Connection.

## 4. <u>Photo of modified set:</u>

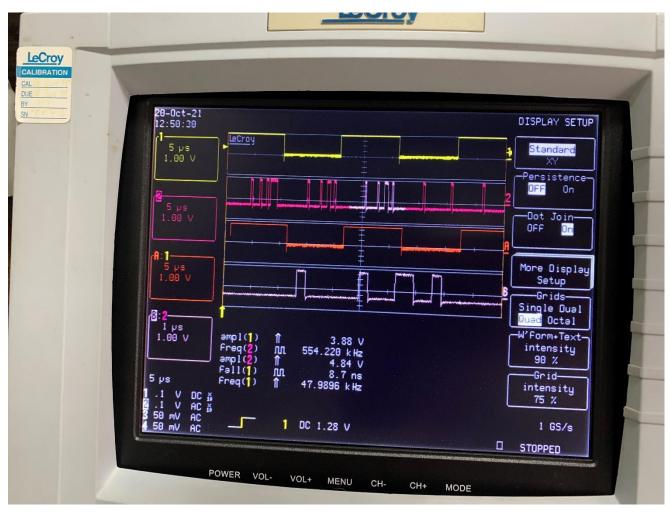

Scope show CN501 work clock pin 1 and data lines pin 2 and pin 5.

## 5. YM3436 Datasheet:

### 6. Draft Notes:

DA8X draft notes.pdf Update V4:

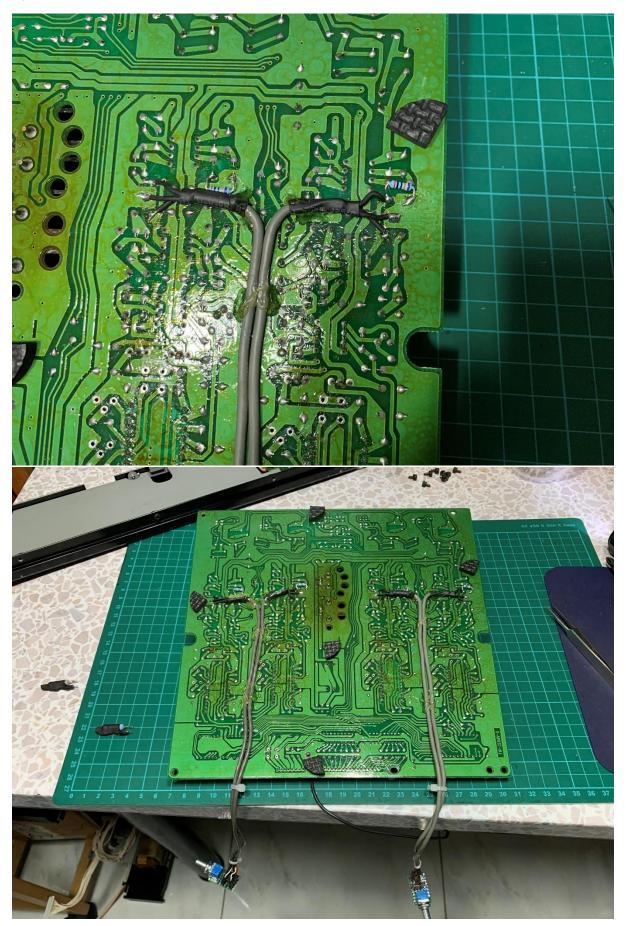

About picture shown two resistors at the power supply to the DAC board. The resistor value is as below: Purpose is to drop the voltage from 24V to about +/-19V at the input of 7815 and 7915 voltage regulators. As you can see at other photos that they are overheated and the PCB already turned brownish color due to prolong use! I think it is one of the design faults for this DAC!

+24V – about (10 + 18) ohm 3W each.

-24V – about 20 ohm 3W or higher resistor.

Before I use resistor to drop the voltages, I add the height of heatsink and use a thermal pad at the top cover to transfer some of the heat to the casing top. It seems not effective and thus I add voltage drop resistor above. A final solution will be add a fan but it may introduce noise!

Note: I removed all the trimmer pots at the PCM63 due to they are not original and I do not have enough equipment to tune the distortion yet. May be I shall put back and tune them in future!

Enjoy Music! Spencer Cheung Date: Oct 28, 2021 (V3) Revised on 30 Nov (V4) Copyright.